# **A1 DIGITAL DATA TRANSMISSION SYSTEM** WORD GENERATOR CIRCUIT SD-1G097-01 ANALYSIS AND CLEARANCE OF TROUBLE

#### 1. GENERAL

1.01 This section describes methods and procedures to be followed in the analysis and clearance of typical troubles which may be encountered in the word gen-erator circuit, SD-16097-01.

1.02 These trouble indications usually occur from failure to meet the test and adjust-

ment requirements described in Section 314-505-501 covering out-of-service tests of the word generator. The suggested procedures for location of the troubles are classified in the same order as the requirements listed in Section 314-505-501 under the following headings.

- A. Binary CountersB. Dipulse OutputC. Synchronization

Under the following heading, Tables A through 0 are found. These tables may be used to locate a defective variator.

D. Varistor Tables

1.03 Care should be used to prevent damage to varistors by avoiding the direct application of the heat of a soldering iron.

1.04 Reference to schematic SD-1G097-01 will be helpful in applying the procedures of this section.

- 2. APPARATUS

- 2.01 KS-16305 Waterman oscilloscope.

- 2.02 No. 262B plug (600 ohms).

- 2.03 One Vector tube socket adapter, T-9-N or CBS Hytron SH29, or equivalent.

- 3. TROUBLE CONDITIONS

#### A. Binary Counters

3.01 When a square wave cannot be obtained at BCAl test point in accordance with the requirements of Test A, Step 19, of Section 314-505-501, it is probably due to one of the following reasons.

(a) No sine wave at the OSC test point, which may be due to:

(1) Defective crystal in the oscillator circuit, Fig. 4.

(2) Faulty Q1, Q2, Q3, or Q4 transistor or CR1 or CR2 variator in the oscillator circuit, Fig. 4.

(3) Faulty V16 electron tube.

(b) No square wave at pin 4 of V5 electron tube. (Use T-9-N adapter.) This may be due to faulty V4 or V5 electron tube.

(c) A square wave at pin 4 of V5 electron tube but not at the BCAl test point may be due to:

- (1) Faulty V6 or V17 electron tube.

- (2) Defective CR201-1, CR202-1, or CR203-1 varistor in Fig. 1.

3.02 When a rectangular pulse cannot be obtained at the ST test point to meet the requirements of Test A, Step 21, of Section 314-505-501, it is probably due to one of the following reasons.

- (a) A BCA- counter may be faulty if a square wave is not obtained at each of the BCA- test points. Starting at the lowest numbered BCA- counter and continuing in order, this condition may be due to:

- (1) Faulty V6 or V17 electron tube or CR201-1, CR202-1, or CR203-1 varistor in BCAl counter.

- (2) Faulty V7 or V18 electron tube or CR201-2, CR202-2, or CR203-2 varis-tor in BCA2 counter.

- (3) Faulty V8 or V19 electron tube or CR201-3, CR202-3, or CR203-3 varis-tor in BCA3 counter.

- (4) Faulty V9 or V20 electron tube or CR201-4, CR202-4, or CR203-4 varis-tor in BCA4 counter.

(b) No square pulse at pin 3 of the V24 electron tube may be due to an open CR25 varistor in the word matrix circuit, Fig. 5.

(c) No square pulse at pin 4 of the V24 electron tube may be due to a faulty V24 electron tube.

© American Telephone and Telegraph Company, 1957 Printed in U.S.A.

#### SECTION 314-505-301

1.

(d) No square pulse at pin 4 of the V22 electron tube may be due to a faulty

V24 electron tube.

- (e) No square pulse at pin 4 of V12 electron tube may be due to a faulty

V4 or V12 electron tube or a defective

varistor, CR1 through CR6, in the sampling gate, Fig. 2.

- (f) No square pulse at the ST test point may be due to a faulty Vl electron tube.

3.03 When a square pulse cannot be obtained at the DAT test point to meet the requirements of Test A, Step 23, of Section 314-505-501, it is probably due to one of the following reasons.

- (a) A square pulse at pin 7 of the V29 electron tube and not at pin 8 may be due to a faulty V29 electron tube.

- (b) If a square pulse appears at pin 8

of V29 electron tube and not at pin 7

of V24 electron tube, refer to Tables

F and G.

- (c) No square pulse at pin 6 of V24

electron tube may be due to a faulty

V24 electron tube.

- (d) No square pulse at pin 4 of V23 electron tube may be due to a faulty

V23 electron tube.

(e) No square pulse at pin 4 of V13 electron tube may be due to a faulty V4 or V13 electron tube or a defective varistor, CR7 through CR12, in the sampling gate circuit, Fig. 2.

(f) No square pulse at the DAT test point may be due to a faulty V2 electron tube.

3.04 Inability to remove two of the pulses when Sl switch is operated to position 32, as stated in Test A, Step 26, of Section 314-505-501, is probably due to one of the following reasons.

(a) No square wave at the BCBl test point may be due to a faulty V10 or V27

electron tube or CR301-1, CR302-1, or CR303-1 varistor in the BCBl counter.

(b) If a square wave appears at the BCB1 test point and the circuit is still not functioning properly, it may be due to an open CR8 varistor in Fig. 1.

3.05 Inability to remove pulses when Sl switch is operated to other positions as stated in Test A, Steps 28 to 31, inclusive, of Section 314-505-501, is probably due to one of the following reasons.  (a) No square wave at the BCB- test point. This may be due to:

(1) Faulty V11 or V27 electron tube or CR301-2, CR302-2, or CR303-2 variator if no square wave appears at the BCB2 test point.

(2) Faulty V21 or V28 electron tube or CR301-3, CR302-3, or CR303-3 varistor if no square wave appears at the BCB3 test point.

(3) Faulty V31 or V28 electron tube or CR301-4, CR302-4, or CR303-4 varistor if no square wave appears at the BCB4 test point.

(b) When a square wave is obtained at the BCB- test point and the circuit is still not functioning properly, the trouble may be due to an open variator, CR9, CR10, or CR11, of Fig. 1, corresponding to counters BCB2, BCB3, or BCB4, respectively.

B. Dipulse Output

3.06 When dipulses cannot be made to meet the requirements of Test B, Step 20, of Section 314-505-501 by adjusting the LEVEL potentiometer, it is probably due to one of the following reasons.

(a) If a dipulse does not appear at the data output jack, or if the 1/2-inch peak-to-peak deflection cannot be met, it may be due to a faulty V26 electron tube or a defective variator. (See Tables B through I.)

(b) If the dipulse is misshapen and replacing the V26 electron tube does not eliminate the trouble, refer to Table J, L, N, or O.

3.07 When the requirements of Test B, Steps 22 through 26, of Section 314-505-501 cannot be met because no dipulse or more than one dipulse appears corresponding to each operated switch, it may be due to a faulty varistor in the word forming network. Locate by referring to Tables B through I.

3.08 When the requirements of Test B, Step 28, of Section 314-505-501 cannot be met because no dipulse or more than one dipulse appears, it may be due to a faulty varistor.

Refer to Table A. If the start pulse is misshapen, refer to Tables K and M.

3.09 If the sine wave described in Test B, Step 30, of Section 314-505-501 cannot be obtained, or the 1/2-inch peak-to-peak amplitude cannot be attained, it is probably due to one of the following reasons.

- (a) Faulty V16 or V26 electron tube.

- (b) Shorted CR6 or CR7 varistor in Fig. 1.

Page 2

#### C. Synchronization

3.10 If the matching and error counter circuit records errors, failing to meet the requirements of Test C, Step 21, of Section 314-505-501, it is because word generators 1 and 2 are not in synchronism. This condition may be due to one of the following reasons.

- (a) Faulty V4, V15, or V25 electron tube.

- (b) Defective CR3, CR4, or CR5 variator in Fig. 1.

#### D. Varistor Tables

3.11 The following tables provide the necessary information to locate an open or shorted variator in the word generator.

3.12 The following oscilloscope adjustments are to be made before tables are

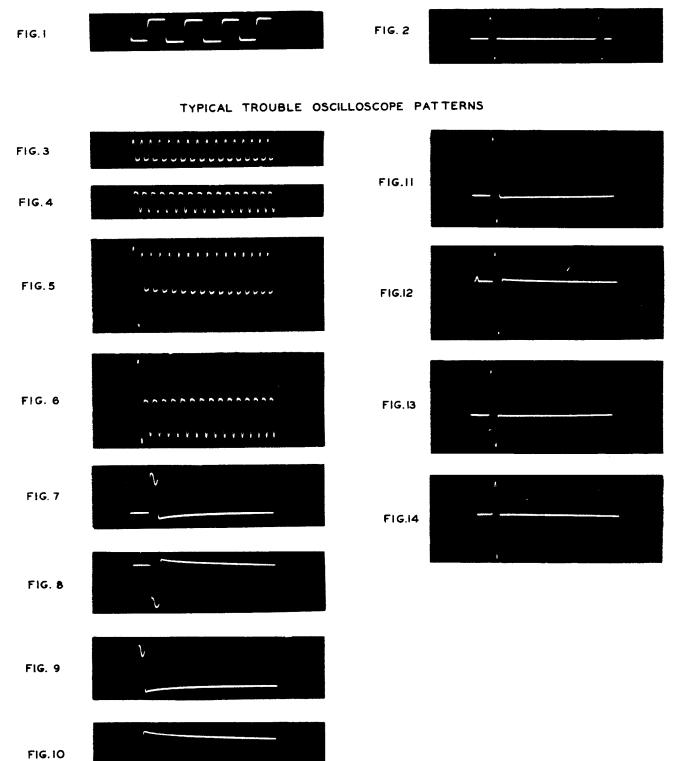

used. Connect oscilloscope SYNC input to word generator SYNC test point, set SYNC-SEL switch to TRIG EXT HI, insert oscilloscope probe into BCA2 test point, and adjust sweep to obtain four cycles of square wave (Fig. 1).

3.13 Sl switch of the word generator should be in position 16.

3.14 The data output jack or start output jack referred to in the tables are the ones located in the jack and connector circuit or in the word generator.

3.15 All observations will be made at the data output jack, unless otherwise specified.

3.16 While using tables, oscilloscope is to be terminated in 600 ohms.

3.17 In reference to the Bits Appear column of tables, the diagram belowwill show the position of bits on oscilloscope.

#### Position

ST B1 B2 2 3 4 5 6 7 8 9 10 11 12 B3 B4

(That is, see Fig. 2 which shows bits in positions [Pos] B2 and B3.)

3.18 To illustrate the use of the tables, an example will be given. Assume that observations are being made at the data output jack. S2 switch is operated down and bits appear in positions 2 and 6. Looking at the start output jack, it is found that the start pulse is not normal; bits appear in positions ST, Bl, B2, 2,3, 4, 5, and 6. Refer to Table A and under the Switches Operated column it is indicated that no switches are to be operated. Therefore, restore S2 switch to its up position. It is observed that bits still appear in positions ST, Bl, B2, 2, 3, 4, 5, and 6 at the start jack. Since this combination is not listed in the Bits Appear column of Table A, go on to Table B. To use Table B, observations are made at the data output jack with no switches operated down. Looking at the data output jack with all switches in the up position, it is found that no bits appear. Therefore, Table B does not apply. Table C requires that the start pulse be normal and, therefore, Table C does not apply. Since the operation of S2 switch produced the trouble condition, looking down the Switch Operated column of Table D, it is found that S2 switch appears twice. The first appearance of S2 lists bits appearing in positions Bl and 2. The second appearance of S2 lists bits appearing in positions B2 and 2. Therefore, Table D does not apply since it was originally determined that the operation of S2 switch produced bits in positions 2 and 6. Table E has S2 and S3 switches operated in all rows. Therefore, operate S2 and S3 switches which will result in bits in positions 2, 3, 4, 5, and 6. In the Bits Appear column, this combination of bits appears when CR21 variator of Fig. 4 is shorted. Hence, the trouble has been located.

TABLE A

| Switches<br>Operated | Bits                                    | This Varistor<br>in Fig. 4 |

|----------------------|-----------------------------------------|----------------------------|

| Down                 | Appear                                  | Open                       |

| <u></u>              | - <u></u>                               |                            |

| None                 | Pos ST,7                                | CR21                       |

| None                 | Pos ST,3                                | <b>CR22</b>                |

| None                 | Pos ST, B2                              | CR23                       |

| None                 | Pos ST,Bl                               | CR24                       |

|                      | b <b>serv</b> ations ar<br>output jack. | e to be made at            |

observation at the data output jack while

using Table A will appear normal.

Page 3

### SECTION 314-505-301

1

|                              | TABL                                                    | ЕВ                                                    |                                                               |                                            | TABLE D                                                        |                                                      |

|------------------------------|---------------------------------------------------------|-------------------------------------------------------|---------------------------------------------------------------|--------------------------------------------|----------------------------------------------------------------|------------------------------------------------------|

| Switches<br>Operated         | Bits                                                    | This<br>Varistor<br>in<br>Fig. 4                      | ,                                                             | Switche<br>Operate<br><u>Down</u>          |                                                                | This Varistor<br>in Fig. 4<br>Open                   |

| <u>Down</u>                  | Appear                                                  | Shorted                                               | Remarks                                                       | 5<br>9                                     | Pos 3,5<br>Pos 7,9                                             | CR12                                                 |

| None                         | Pos ST,Bl,<br>3,4,7,8,<br>11,12                         | CR9 or<br>CR10                                        | To determine<br>which varis-<br>tor is shorted,               | 5                                          | Pos 5,6<br>Pos 9,10                                            | CR13                                                 |

|                              |                                                         |                                                       | observe di-<br>pulse at start<br>output jack.<br>If double    | 2<br>6<br>10                               | Pos B1,2<br>Pos 4,6<br>Pos 8,10                                | CR11                                                 |

|                              |                                                         |                                                       | start pulse<br>appears, CR10<br>is shorted.                   | 2<br>6<br>10                               | Pos B2,2<br>Pos 5,6<br>Pos 9,10                                | CR15                                                 |

| None                         | Pos B2,2,<br>5,6,9,10,<br>B3,B4                         | CR11 or<br>CR12                                       |                                                               | 3<br>7<br>11                               | Pos 3, <b>5</b><br>Pos 7,9<br>Pos 11,B3                        | CR10                                                 |

| None                         | Pos ST,B2,<br>3,5,7,9,<br>11,B3                         | CR13 or<br>CR14                                       | To determine<br>which varis-<br>tor is shorted,               | 3<br>7<br>11                               | Pos 3,4<br>Pos 7,8<br>Pos 11,12                                | CR14                                                 |

|                              |                                                         |                                                       | observe di-<br>pulse at start<br>output jack.<br>If a start   | 4<br>8<br>12                               | Pos 4,6<br>Pos 8,10<br>Pos 12,B4                               | CR9                                                  |

|                              |                                                         |                                                       | pulse, a blank,<br>and another<br>start pulse<br>appear, CR14 | 4<br>8<br>12                               | Pos 3,4<br>Pos 7,8<br>Pos 11,12                                | CR16                                                 |

| Nono                         |                                                         | (D) (                                                 | is shorted.                                                   | L                                          | TABLE E                                                        |                                                      |

| None                         | Pos B1,2,<br>4,6,8,10,<br>12,B4                         | CR15 or<br>CR16                                       |                                                               | All swite                                  | hes in a group must                                            | t be operated.                                       |

|                              | TABL                                                    | E C                                                   |                                                               | Switches<br>Operated<br>Down               | Bits<br>Appear                                                 | This<br>Varistor<br>in Fig. 4<br><u>Shorted</u>      |

| Switches<br>Operated<br>Down |                                                         | This<br>Varis-<br>tor in<br>Fig. <sup>1</sup><br>Open | - Varis-<br>h tor in<br>4 Fig. 4                              | 2,3<br>2,3<br>2,3<br>2,3                   | Pos 2,3,4,5,6<br>Pos 2,3,10<br>Pos 2,3,4,11<br>Pos 2,3,5,11,B3 | CR21<br>CR22<br>CR23<br>CR24                         |

| 2<br>2<br>3                  | Pos 2,10<br>Pos 2,6<br>Pos 3,11                         | CR1<br>CR5                                            | CR5<br>CR1                                                    | L                                          | TABLE F                                                        |                                                      |

| <u> </u>                     | Pos 4,12<br>Pos 5,B3                                    | CR2                                                   | CR7                                                           | All swite                                  | ches in a group mus                                            | t be operated.                                       |

| 56 34 56 78 9                | Pos 6,B4<br>Pos ST,3<br>Pos Bl,4<br>Pos B2,5<br>Pos 2,6 | CR7                                                   | CR2                                                           | Switches<br>Operated<br><u>Down</u><br>5,9 | Bits<br><u>Appear</u><br>Pos 5                                 | This<br>Varistor<br>in Fig. 1<br><u>Open</u><br>CR19 |

| 7<br>8<br>9                  | Pos ST,7<br>Pos Bl,8<br>Pos B2,9                        | CR3                                                   | CR6                                                           | 2,6,10                                     | Pos 9<br>Pos 6,10                                              | CR15<br>CR12<br>CR16                                 |

| 10<br>7<br>8<br>9            | Pos 2,10<br>Pos 7,11<br>Pos 8,12<br>Pos 9,13            | CR6                                                   | CR3                                                           | 3,7,11                                     | Pos 2,6<br>Pos 3,7                                             | CR20<br>CR21<br>CR13                                 |

| 10<br>11<br>12<br>11         | Pos 10,E<br>Pos 3,11<br>Pos 4,12<br>Pos 7,11            | CR4<br>CR8                                            | с <b>к</b> 8<br>Ск4                                           | 4,8,12                                     | Pos 3,11<br>Pos 4,8<br>Pos 8,12                                | CR17<br>CR22<br>CR14                                 |

| 12<br>Note: S<br>Table C.    | Pos 8,12<br>tart dipulse                                |                                                       | normal to use                                                 | Note: St<br>Table F.                       | Pos 4,12<br>art dipulse must be                                | CR18<br>e normal to use                              |

L

| Switches                | ·              | This Varistor                                                                           |

|-------------------------|----------------|-----------------------------------------------------------------------------------------|

| Operated<br><u>Down</u> | Bits<br>Appear | in Fig. 4<br><u>Open</u>                                                                |

| 5,9                     | None           | CR18<br>Provided a bit ap-<br>pears only in posi<br>tion 2 when S2 is<br>operated down. |

| 2,6,10                  | None           | CR17<br>Provided a bit ap-<br>pears only in posi<br>tion 3 when S3 is<br>operated down. |

| 4,8,12                  | None           | CR19<br>Provided a bit ap-<br>pears only in posi<br>tion 3 when S3 is<br>operated down. |

| 3,7,11                  | None           | CR20<br>Provided a bit ap-<br>pears only in posi<br>tion 3 when S3 is<br>operated down. |

| TA | BL | Æ | J |

|----|----|---|---|

|    |    |   |   |

| Switches<br>Operated<br>Down | Bits<br>Appear                                        | This<br>Varistor<br>in Fig. 3<br>Shorted |

|------------------------------|-------------------------------------------------------|------------------------------------------|

| None                         | Positive half of<br>all bits appear.<br>(See Fig. 3.) | CR2                                      |

| None                         | Negative half of<br>all bits appear.<br>(See Fig. 4.) | CR1                                      |

TABLE K

| Switches<br>Operated<br><u>Down</u> | This<br>Varistor<br>Bits in Fig. 3<br>Appear <u>Shorted</u>                               |

|-------------------------------------|-------------------------------------------------------------------------------------------|

| None                                | Start dipulse CR4<br>and positive half<br>of all other<br>bits appear. (See<br>Fig. 5.)   |

| None                                | Start dipulse CR3<br>and negative<br>half of all<br>other bits ap-<br>pear. (See Fig. 6.) |

| <u>Note</u> : Obs<br>start outp     | ervations are to be made at<br>ut jack.                                                   |

TABLE L

| Switches<br>Operated<br>Down | Bits<br>Appear                                                                                                               | This<br>Varistor<br>in Fig. 3<br><u>Open</u> |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 2                            | Position 2, but it<br>appears as a posi-<br>tive going square<br>wave with a dipulse<br>superimposed on it.<br>(See Fig. 7.) | CR2                                          |

| 2                            | Position 2, but it<br>appears as a nega-<br>tive going square<br>wave with a dipulse<br>superimposed on it.<br>(See Fig. 8.) | CR1                                          |

TABLE G

TA.

•

TABLE H

| All switches                                                                                                     | in a group must be                                                                                                                                                                                 | e operated.                                                                          |  |

|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|

| Switches<br>Operated<br><u>Down</u>                                                                              | Bits<br>Appear                                                                                                                                                                                     | This<br>Varistor<br>in Fig. 1<br><u>Shorted</u>                                      |  |

| 3,4,7,11<br>3,4,8,12<br>4,5,9<br>2,5,6,10<br>3,7,8,11<br>4,7,8,12<br>5,8,9<br>2,6,9,10<br>3,7,11,12<br>4,8,11,12 | Pos 3,4,7,8,11,12<br>Pos 3,4,7,8,11,12<br>Pos 4,5,8,9<br>Pos B2,2,5,6,9,10<br>Pos 3,4,7,8,11,12<br>Pos 3,4,7,8,11,12<br>Pos 4,5,8,9<br>Pos B2,2,5,6,9,10<br>Pos 3,4,7,8,11,12<br>Pos 3,4,7,8,11,12 | CR13<br>CR14<br>CR15<br>CR16<br>CR17<br>CR18<br>CR19<br>CR20<br>CR20<br>CR21<br>CR22 |  |

| TABLE I                                                                                                          |                                                                                                                                                                                                    |                                                                                      |  |

| All switches | in a group must | be operated.<br>This |

|--------------|-----------------|----------------------|

| Switches     |                 | Varistor             |

| Operated     | Bits            | in Fig. 4            |

| Down         | Appear          | Shorted              |

|              |                 |                      |

| 2 to 12      | Pos 5,9         | CR17                 |

| 2 to 12      | Pos 2,6,10      | CR18                 |

| 2 to 12      | Pos 4,8,12      | CR19                 |

| 2 to 12      | Pos 3,7,11      | CR20                 |

|              |                 |                      |

## SECTION 314-505-301

1.

TABLE M

| Switches<br>Operated<br><u>Down</u> | Bits<br>Appear                                                                                                           | This<br>Varistor<br>in Fig. 3<br>Open |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| None                                | Start pulse ap-<br>pears as a posi-<br>tive going square<br>wave with a dipulse<br>superimposed on it.<br>(See Fig. 9.)  | CR4                                   |

| None                                | Start pulse ap-<br>pears as a nega-<br>tive going square<br>wave with a dipulse<br>superimposed on it.<br>(See Fig. 10.) |                                       |

| <u>Note:</u> Ob<br>start out        | servations are to be<br>put jack.                                                                                        | made at                               |

TABLE N

| Switches<br>Operated<br><u>Down</u> | Bits<br>Appear                                                            | This<br>Varistor<br>in Fig. 3<br>Open |

|-------------------------------------|---------------------------------------------------------------------------|---------------------------------------|

| 2                                   | Position 2, but<br>the dipulse ap-<br>pears unbalanced.<br>(See Fig. 11.) | CR6                                   |

| 2                                   | Position 2, but<br>the dipulse ap-<br>pears unbalanced.<br>(See Fig. 12.) | CR5                                   |

TABLE O

| Switches<br>Operated<br><u>Down</u> | Bits<br>Appear                                                                                  | This<br>Varistor<br>in Fig. 3<br>Shorted |

|-------------------------------------|-------------------------------------------------------------------------------------------------|------------------------------------------|

| 2                                   | Postion 2, but<br>positive half of<br>dipulse is larger<br>than negative hal:<br>(See Fig. 13.) | CR5                                      |

| 2                                   | Position 2, but<br>negative half of<br>dipulse is larger<br>than positive<br>half. (See Fig. 1- | CR6<br>4.)                               |

r

## TYPICAL NORMAL OSCILLOSCOPE PATTERNS

Page 7 7 Pages